# ●µプローブTEG開発

# 区层代介汉

### 研究の概要

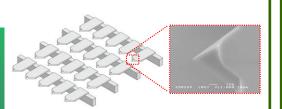

- •マルチプローブアレイデバイスの試作(プローブ先端サブumオーダ / 最先端8"ライン活用)

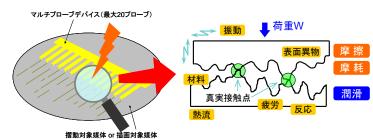

- ・マルチプローブ評価装置によるトライボロジー特性定量評価手法の確立と実践

(シングルプローブ評価系と同等の検出精度/ウェハ内&ロット間バラつき影響調査)

# 技術内容

# "マルチプローブアレイデバイス"

先端サイズがnm級のプローブを 複数並べたデバイス

→ BEANS本体にて対応

# 実用化への課題:

①プローブ先端挙動バラつきの抑制 2プローブ耐摩耗性向上

各プローブ先端のナノトライボロジー現象の把握&制御が必須!

ナノトライ

ボロジー現象

#### "トライボロジー"

物体接触界面現象の総称

挙動バラつきを生む根源!

プローブ製造バラつき

各プローブ間相互作用

摺動条件(速度、荷重etc.)

ナノスケール構造の接触

複数プローブ同時の 定量的評価手法&指針は 世界的にも未確立

#### 用途

マルチプローブ評価装置

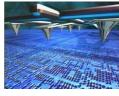

# マルチプローブリソグラフィ装置

- ローコスト微細パターン描画

- 現行EB描画装置の代替

# ・マルチプローブ型情報記録装置

- 超高密度情報記録

- NAND、HDDの記録限界打破

# マルチプローブ顕微鏡

- 超高スループット

# プローブリソグラフィ装置

ローコストで微細描画 数10nm究極リソグラフィ

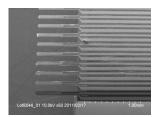

プローブリソグラフィによる描画の一例

#### プローブ型情報記録装置

数Tbit/inch<sup>2</sup>級 ポストNAND フラッシュ&HDD

IBM社"Millipede"

# ●µプローブTEG開発

# 区是代介又

#### 目標:

- 1) **最先端8"ラインによるデバイス試作** (サブumオーダ先端)

- 2) マルチプローブ評価装置によるトライボロジー特性定量評価手法の確立と実践(ウェハ内&ロット間バラつき影響調査)

#### 成果まとめ:

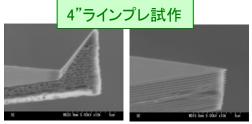

- 1) 4"ライン、最先端8"ラインでのデバイス試作に成功

- → プローブ先端接触点の有効幅サブum

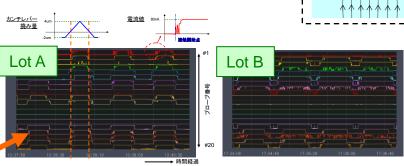

- 2) マルチプローブ先端電流値のリアルタイム計測法を確立

- → 単一プローブ評価系と同等の検出性能を実証

- → 特性バラつき計測に対する有用性を確認

#### 成果の具体的説明

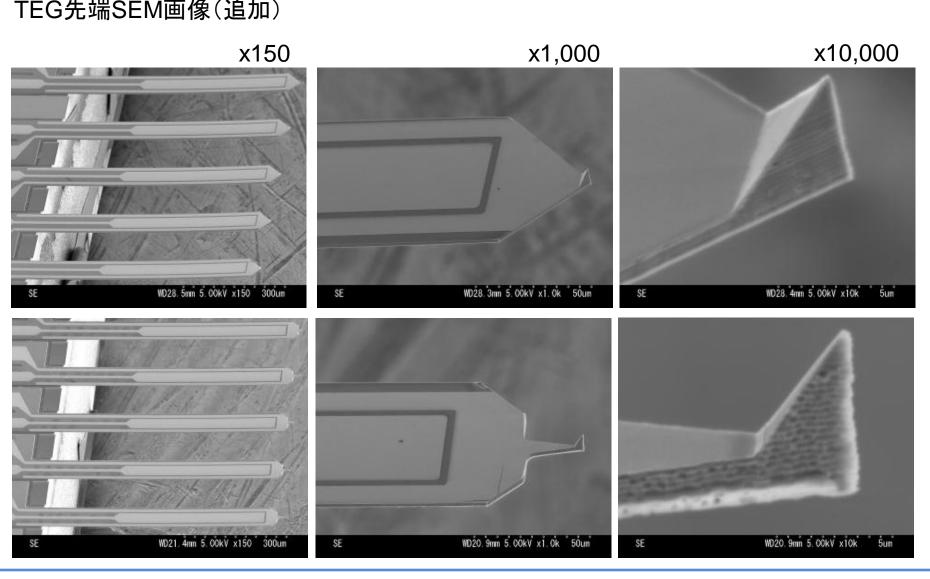

1) デバイス試作

- ・2種のフローによるプロセス最適化

- ・プローブ先端サイズ:サブum

最先端8"ライン試作

・ウェハ内/ロット間バラつき調査に投入

# 2) マルチプローブのトライボロジー評価手法

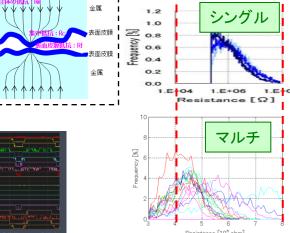

# 電流値リアルタイム計測法:

- 16本のプローブの特性同時計測

- シングルプローブ評価系と 同等の検出レンジを達成

- ロット間特性バラつきの計測に成功

非摺動時電流値の複数プローブー括計測

表面状態・形状・摺動条件に対して 最もセンシティブな<mark>接触抵抗</mark>に着目

抵抗検出レンジ比較

# 実用化への課題:『マルチプローブ先端挙動バラつきの抑制』

- ・バラつき抑制の鍵となるトライボロジー評価プラットフォームを確立

- ・今後の評価計画立案の指針となる実践的評価データを獲得

- → 課題解決に向け大きく前進 (H23年度以降はBEANS本体で開発継続)

# TEG先端SEM画像(追加)

# ●µプローブTEG開発

# 実用化・事業化の見通し

# マルチプローブアレイデバイスの実用化先:

- ①マルチプローブリソグラフィ装置

- (ローコスト微細パターン描画 / 現行EB描画装置の代替)

- ②マルチプローブ型情報記録装置

- (超高密度情報記録 / NAND、HDDの記録限界打破)

- ③マルチプローブ顕微鏡(超高スループット)

#### プローブリソグラフィ装置

ローコスト微細描画 数10nm究極 リソグラフィ

#### プローブ型情報記録装置

数Tbit/inch2級 ポストNAND フラッシュ&HDD

マルチプローブ顕微鏡 高スループット

プローブ先端電流値の 複数プローブ同時リアルタイム計測

# ①:マルチプローブリソグラフィ装置の実用化に向けたステップ

16nm世代以降の半導体・MEMS向けローコスト

描画技術として、実用化・事業化を目指す

【課題1】マルチプローブ先端挙動バラつきの抑制

- → H22年度Gデバイス活動:

- プローブ先端電流値リアルタイム計測による特性バラつき評価手法確立。

- ・最先端8"ライン試作評価による基礎データ取得に成功。 H23年度以降BEANS本体活動にフィードバックし、取り組み継続。

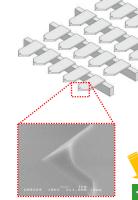

# 【課題2】プローブ先端の耐摺動摩耗性向上

→ 耐摩耗性向上ナノ構造を有するプローブをBEANS本体にて開発中。 H24年度末の基本技術確立を目指す。

最先端8"ラインにて試作した マルチプローブアレイデバイス

耐摩耗プローブ(BEANS本体にて開発中)

参考:(株)東芝 プレスリリース

http://www.toshiba.co.jp/about/press/2011\_01/pr\_j2502.htm